# Switched-RC Radio Frequency N-Path Filters

**Amir Ghaffari**

# SWITCHED-RC RADIO FREQUENCY N-PATH FILTERS

Amir Ghaffari

#### The Graduation Committee:

**Chairman:** Prof.dr.ir. A.J. Mouthaan University of Twente

Secretary: Prof.dr.ir. A.J. Mouthaan University of Twente

**Promoter:** Prof.dr.ir. B. Nauta University of Twente

**Assistant Promoter:** Dr.ing. E.A.M. Klumperink University of Twente

#### **Members:**

Prof.dr.ir. F.E. van Vliet University of Twente

Prof.dr.ir. C.H. Slump University of Twente

Prof.dr.ir. A.H.M. van Roermund Eindhoven University of Technology

Prof. A. Kaiser Lille Catholic University/ISEN

CTIT Ph.D. Thesis Series No. 13-244 Center for Telematics and Information Technology P.O. Box 217, 7500 AE Enschede, The Netherlands

This research is supported by the Dutch Technology Foundation (STW), which is part of the Netherlands Organization for Scientific Research (NWO) and partly funded by the Ministry of Economic Affairs, Agriculture and Innovation.

Center for Array Technology

**Title:** Switched-RC Radio Frequency N-Path Filters

**ISBN:** 978-90-365-3519-9

ISSN: 1381-3617

**DOI:** 10.3990/1.9789036535199

© 2013, Amir Ghaffari, Enschede, The Netherlands.

# SWITCHED-RC RADIO FREQUENCY N-PATH FILTERS

#### DISSERTATION

to obtain

the degree of doctor at the University of Twente, on the authority of the rector magnificus,

Prof. dr. H. Brinksma,

on account of the decision of the graduation committee

to be publicly defended

on Wednesday 27<sup>th</sup> March 2013 at 14.45

by

Amir Ghaffari

born on 1<sup>st</sup> September 1980 in Oroumieh, Iran This dissertation has been approved by:

Promoter: Prof.dr.ir. B. Nauta

Assistant Promoter: Dr.ing. E.A.M. Klumperink

## Samenvatting

Afstembare filters zijn zeer gewenst voor mobiele radio communicatie en de wens bestaat deze op chip te realiseren samen met de overige benodigde zend- en ontvangst hardware. Vooral nu mobiele apparaten vele verschillende draadloze communicatie mogelijkheden dienen te ondersteunen (denk bv. aan GSM, Bluetooth, WiFi, UMTS) geïntegreerd op één chip, is er dringend behoefte aan afstembare filters. Ook groeit het mobiele internet gebruik enorm, zodat behoefte bestaat aan programmeerbare radio hardware die op een slimmere manier met het schaars beschikbare radio spectrum omgaat. Dit heeft geleid tot het concept van een "cognitieve radio", een stuk radio hardware dat op een intelligente manier dynamisch het spectrum gebruikt. Zo'n cognitieve radio vraagt om flexibel programmeerbare afstembare filters en meer algemeen "software defined radio" (SDR) hardware.

Het beperkte dynamische bereik van radio ontvangers vraagt om filtering van het radiosignaal direct bij de antenne. Dit filter dient de sterke ongewenste stoorsignalen te onderdrukken, die anders de radio ontvanger zodanig zouden oversturen dat door sterke vervorming betrouwbare draadloze communicatie onmogelijk wordt. Traditioneel wordt de filtering geïmplementeerd via aparte zgn. Surface Acoustic Wave (SAW) filters of Bulk Acoustic Wave (BAW) filters. Deze zijn echter relatief groot en duur vergeleken met een schakeling op een chip. Bovendien zijn ze voor een SDR grotendeels ongeschikt, daar ze een vaste (niet-afstembare) filter overdracht hebben. Op chip kunnen weliswaar LC filters gerealiseerd worden maar de kwaliteitsfactor Q van geïntegreerde spoelen is problematisch laag, terwijl "Qenhancement" en "gm-C" filter technieken een te beperkt dynamisch bereik hebben. Er bestaat dus een duidelijke onderzoek uitdaging om tot integreerbare flexibel programmeerbare filters te komen met een groot dynamisch bereik.

In dit proefschrift worden zogenaamde "N-path" filters op basis van geschakelde RC circuits onderzocht. Deze filters gedragen zich als resonator voor frequenties rond hun schakelfrequentie, waarbij het mogelijk is zeer selectieve banddoorlaat of bandrejectie filters te maken. Het N-path filter concept past goed bij SDR omdat de filter frequentie digitaal te programmeren is via de schakelfrequentie, d.w.z. via een

digitale programmeerbare klokfrequentie. Omdat nieuwe CMOS technologieën meer capaciteit per oppervlakte kunnen bieden, terwijl MOS schakelaars een lagere weerstand met minder parasitaire capaciteit kunnen hebben, profiteren N-path filters van Moore's law.

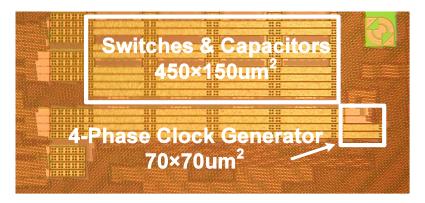

Om de haalbaarheid van N-path filter voor SDR aan te tonen, is een 4-path differentieel switched RC banddoorlaat filter gerealiseerd, een 8-path single-ended filter en ook een differentieel bandstop (notch) filter, alle in 65nm CMOS technologie. Via mathematische analyse zijn de relevante filter overdrachten en ook diverse imperfecties geanalyseerd voor zowel N-path banddoorlaat en notch filters. Het geïmplementeerde banddoorlaat filter vertoont een gemeten IIP3<sub>in-band</sub>>+14 dBm met een compressie punt P<sub>1dB,in-band</sub>>0 dBm en een noise figure <6 dB. Het filter is afstembaar van 0.1-1 GHz. Voor het 8-path notch filter zijn de gemeten IIP3<sub>in-band</sub>>+17 dBm, P<sub>1dB,in-band</sub>>2 dBm, NF<3 dB, terwijl de notch frequentie afstembaar is van 0.1-1.2 GHz met een rejectie van >20 dB. Vooral het compressie punt en de IIP3 zijn veel hoger dan wat typisch met RF CMOS radio ontvangers mogelijk is.

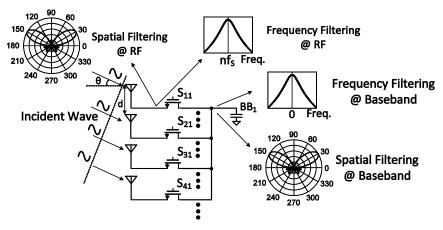

De N-path filter techniek kan ook toegepast worden om spatiële filtering te realiseren. Dit is aangetoond door een 4-element phased-array bundelvormingssysteem te ontwerpen en realiseren. De 8-fase mixers transleren zowel de spatiële- als frequentie-domein filtering van basisband naar radio frequenties op de antenne ingang. Daardoor wordt een opvallend hoog compressie punt van tot wel +10 dBm gehaald voor signalen die buiten de band of antenne bundel vallen.

De N-path filter technieken die in dit proefschrift beschreven worden profiteren van CMOS schaling. Ze maken het mogelijk zeer lineaire afstembare filters te realiseren op een chip, en kunnen een sleuteltechnologie worden voor het realiseren van compacte flexibel programmeerbare radio ontvangst hardware.

### **Abstract**

Tunable on-chip Radio Frequency (RF) filtering is highly desirable for cost effective wireless communication devices. As mobile wireless devices increasingly support multiple RF-bands, tunable RF filtering is wanted. The tremendous growth of wireless communication combined with scarcely available spectrum asks for new, more programmable radio hardware. This has led to the concept of a cognitive radio capable of smart dynamic spectrum access (DSA) which asks for software-defined radio (SDR) hardware, with flexibly programmable tunable filtering.

The limited dynamic range of a receiver front-end dictates the application of RF pre-filtering in front of the receiver, immediately at the antenna. This filter should reject strong out-of-band interfering signals that would otherwise block the receiver or would cause distortion components impeding reliable detection of a desired signal. Traditionally, discrete surface acoustic wave (SAW) or bulk acoustic wave (BAW) filters have been utilized as RF pre-filters. However, this adds to the size and cost of the total system. Even more problematic for cognitive radio, these filters are hardly tunable. State of the art on-chip LC filter techniques are typically limited by the low Q of spiral inductors or by the limited dynamic range in case of active Q-enhanced and gm-C filters. Hence, there is clearly an RF pre-filter research challenge.

In this thesis N-path switched-RC circuits are explored, aiming for RF prefiltering for wireless transceivers. Around the switching frequency, these circuits can be modeled as a resonator and inductor-less high-Q band-pass or band-stop filtering is possible. The filter concept fits well to SDR as the center frequency is programmable by the switching frequency, i.e. via a digital clock. As new CMOS technologies provide higher density capacitors and MOS switches with low onresistance and low parasitic capacitance, N-path filtering benefits from Moore's law.

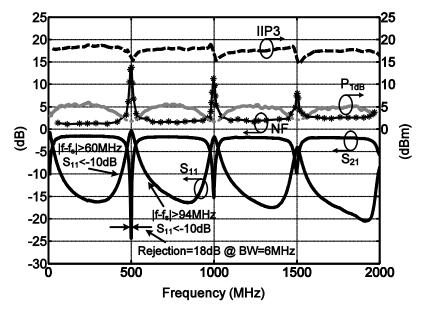

To demonstrate feasibility, a 4-path differential switched-RC bandpass filter, an 8-path single-ended, as well as an 8-path differential bandstop (notch) filter have been implemented in 65nm CMOS technology. A mathematical analysis is presented to describe the filtering behavior as well as various imperfections for the N-path bandpass and notch filters. The implemented bandpass filter provides an in-band input referred third order intercept point IIP3 $_{\text{in-band}}$ >+14 dBm with compression point P<sub>IdB,in-band</sub>>0 dBm at a noise figure NF<6 dB. The filter is tunable from 0.1-1 GHz.

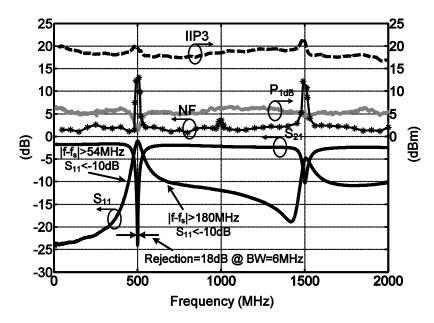

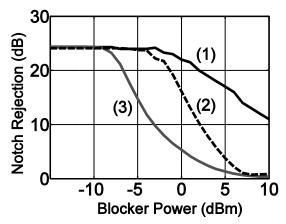

For the 8-path notch filters, IIP3<sub>in-band</sub>>17 dBm,  $P_{1dB,in-band}>2$  dBm and NF<3 dB are achieved while the notch frequency is tunable from 0.1-1.2 GHz with the rejection of >20 dB. Especially the compression point and IIP3 are much higher than what is typically achieved with RF CMOS receivers.

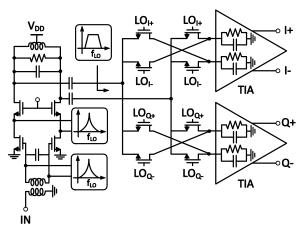

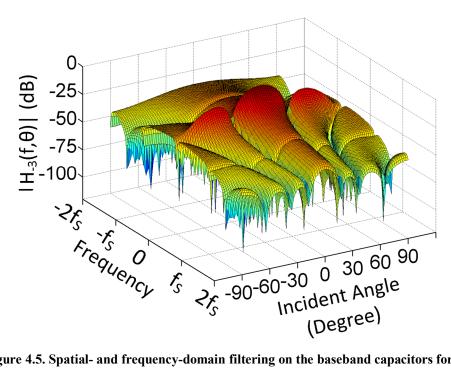

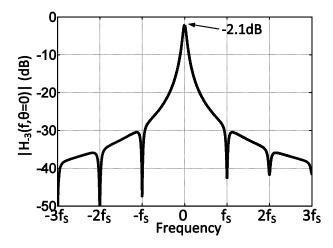

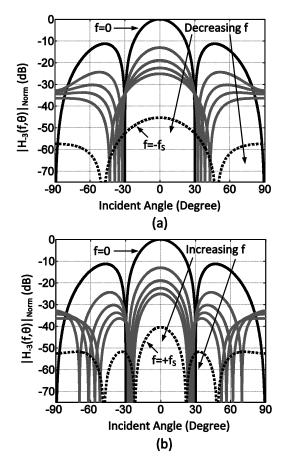

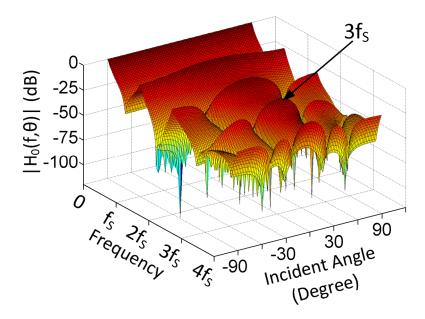

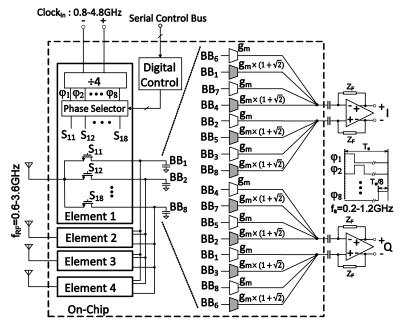

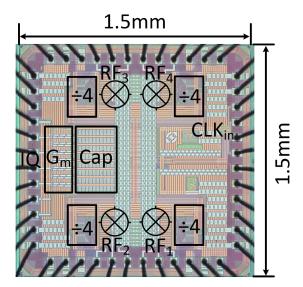

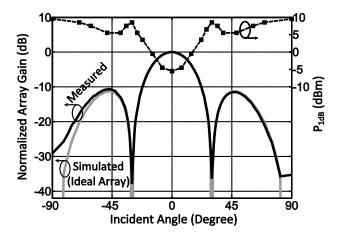

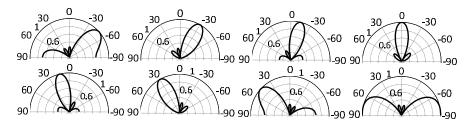

The N-path filtering technique can also be applied for spatial filtering purposes. A 4-element phased-array system has been implemented in 65nm CMOS technology. 8-phase passive mixers translate the Spatial- and frequency-domain filtering from baseband to RF frequencies at the antenna inputs. As a result a remarkable input compression point  $P_{1dB}$  of up to +10 dBm is achieved for out-of-band/beam<sup>1</sup> blockers.

The N-path RF filtering techniques which are discussed in this thesis benefit from CMOS scaling. They present highly linear and tunable filters and pave the way to realize more compact and versatile RF transceivers.

\_

<sup>&</sup>lt;sup>1</sup> This includes two measurement cases: (1) In-beam and out-of-band (2) In-band and out-of-beam blockers.

## **Contents**

| Samenva             | atting                                                    | i   |

|---------------------|-----------------------------------------------------------|-----|

| Abstract            | t                                                         | iii |

| Chapter             | 1 Introduction                                            | 1   |

| 1.1                 | Wireless Transceivers and Filtering                       | 1   |

| 1.2                 | Tunable Filter Application Perspectives                   | 4   |

| 1.2                 | .1 Multi-Band Multi-Standard Transceivers                 | 4   |

| 1.2                 | .2 Software Radio and Software-Defined Radio              | 4   |

| 1.2                 | .3 Cognitive Radio                                        | 6   |

| 1.3                 | RF Pre-Filtering for Dynamic Spectrum Access              | 7   |

| 1.4                 | RF Tunable Filtering Possibilities                        | 9   |

| 1.5                 | Frequency Translated N-Path Filtering                     | 11  |

| 1.6                 | Research Objectives                                       | 15  |

| 1.7                 | Thesis Organization                                       | 16  |

| 1.8                 | References                                                | 17  |

| Chapter<br>Verifica | • •                                                       |     |

| 2.1                 | Introduction                                              | 25  |

| 2.2                 | N-Path Bandpass Filter Concept                            | 27  |

| 2.2                 | .1 Single-Ended Switched-RC N-Path Filter                 | 27  |

| 2.2                 | .2 Differential Switched-RC N-Path Filter                 | 28  |

| 2.3                 | Analysis                                                  | 29  |

| 2.3                 | .1 State-Space Analysis of LPTV circuits                  | 29  |

| 2.3                 | .2 Analysis of the Differential Single-Port N-path Filter | 31  |

| 2.4                 | Characteristics of a Differential N-path Filter           | 34  |

| 2.4              | 4.1 | Filtering and Harmonic Folding Back Effects                    | 34 |  |

|------------------|-----|----------------------------------------------------------------|----|--|

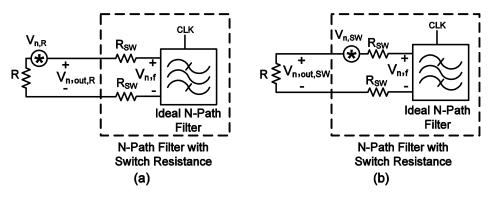

| 2.4              | 4.2 | The Effect of the Switch Resistance                            |    |  |

| 2.4              | 4.3 | Harmonic Selectivity in an N-path Filter                       |    |  |

| 2.4              | 4.4 | Input Impedance of an N-path Filter                            | 40 |  |

| 2.4              | 4.5 | The Effect of the Duty-Cycle of the Clock                      | 41 |  |

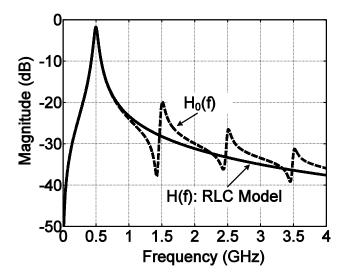

| 2.4              | 4.6 | RLC Model, Bandwidth and Quality Factor                        | 42 |  |

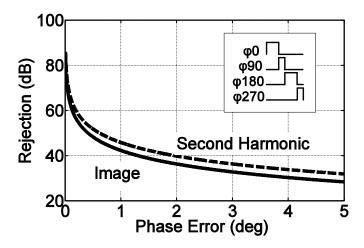

| 2.4              | 4.7 | Imbalance Multiphase Clocking and Mismatch in the Paths        | 44 |  |

| 2.4              | 4.8 | Noise Analysis                                                 | 45 |  |

| 2.5              | Im  | plementation of a 4-Path Differential Bandpass Filter          | 47 |  |

| 2.6              | Мє  | easurement Results and Comparison                              | 49 |  |

| 2.7              | Co  | nclusions                                                      | 56 |  |

| 2.8              | Re  | ferences                                                       | 57 |  |

| Chapte<br>Modeli |     | Tunable N-Path Notch Filters for Blocker Supprend Verification |    |  |

| 3.1              | Int | roduction                                                      | 59 |  |

| 3.2              | N-  | Path Notch Filter Concept                                      | 62 |  |

| 3.3              | Ma  | nthematical Analysis                                           | 64 |  |

| 3                | 3.1 | State-Space Analysis                                           | 64 |  |

| 3                | 3.2 | RLC Model for Single-Ended Notch Filter                        | 68 |  |

| 3.4              | No  | n-Idealities                                                   | 70 |  |

| 3.4              | 4.1 | Switch Resistance and Clock Rise and Fall Times                | 70 |  |

| 3.4              | 4.2 | Harmonic Mixing                                                | 71 |  |

| 3.4              | 4.3 | Noise Analysis                                                 | 73 |  |

| 3.4              | 4.4 | Mismatch and Phase Imbalance                                   | 75 |  |

| 3.5              | Im  | plementation of 8-Path Notch Filters                           | 75 |  |

| 3.6              | Me  | easurement Results and Comparison                              | 79 |  |

| 3.7              | Co  | nclusions                                                      | 85 |  |

| 3.8              | Re  | ferences                                                       | 85 |  |

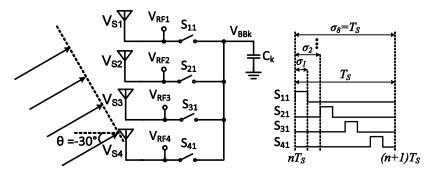

| Chapter 4<br>and Freq | 4 A 4-Element Phased-Array System with Simultaneous uency-Domain Filtering at the Antenna Inputs | •   |

|-----------------------|--------------------------------------------------------------------------------------------------|-----|

| 4.1                   | Introduction                                                                                     | 89  |

| 4.2                   | Multi-Antenna Phased-Array System                                                                | 91  |

| 4.3                   | Mixer-First Phased-Array Architecture                                                            | 93  |

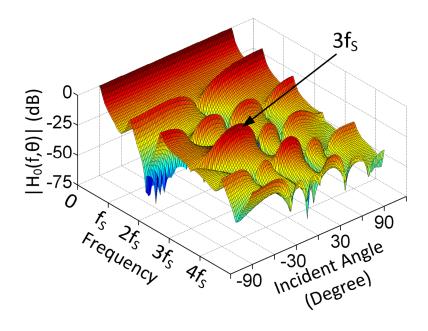

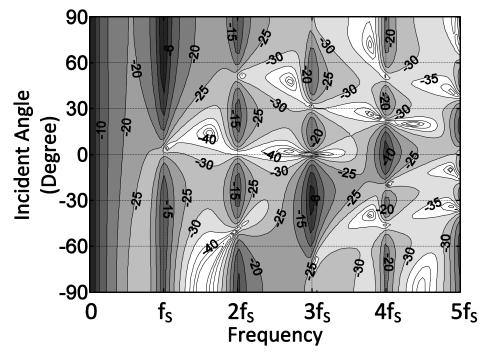

| 4.3.1                 | Spatial- and Frequency-Domain Filtering                                                          | 93  |

| 4.3.2                 | 2 Spatial Angular Resolution                                                                     | 95  |

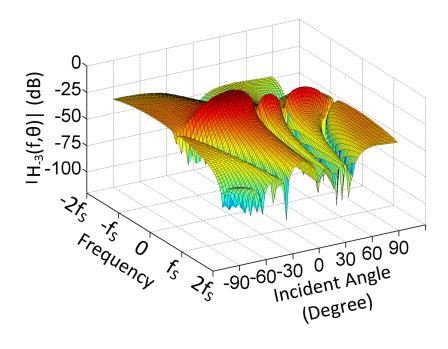

| 4.4                   | Analysis                                                                                         | 96  |

| 4.4.1                 | Baseband Analysis at Zero Incident Angle                                                         | 96  |

| 4.4.2                 | Analysis at the Antenna Inputs for Zero Incident Angle                                           | 101 |

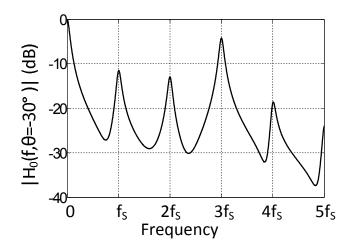

| 4.4.3                 | Baseband Analysis for θ=-30° of Incident Angle                                                   | 103 |

| 4.4.4                 | Analysis at the Antenna Inputs for $\theta$ =-30° of Incident Angle                              | 104 |

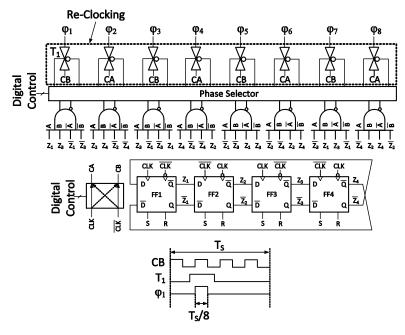

| 4.5                   | Implemented Architecture                                                                         | 107 |

| 4.6                   | Analysis Implications                                                                            | 110 |

| 4.6.1                 | Conversion Gain                                                                                  | 110 |

| 4.6.2                 | 2 Input Power Matching                                                                           | 111 |

| 4.6.3                 | Noise Analysis                                                                                   | 112 |

| 4.7                   | Measurements                                                                                     | 113 |

| 4.8                   | Conclusions                                                                                      | 118 |

| 4.9                   | References                                                                                       | 118 |

| Chapter :             | 5 Conclusions                                                                                    | 121 |

| 5.1                   | Summary and Conclusions                                                                          | 121 |

| 5.2                   | Original Contributions                                                                           | 123 |

| 5.3                   | Future Work                                                                                      | 123 |

| 5.4                   | References                                                                                       | 125 |

| List of Al            | obreviations                                                                                     | 126 |

| Acknowle              | edgements                                                                                        | 128 |

| List of Pu            | ıblications                                                                                      | 130 |

| About the Author131 |

|---------------------|

|---------------------|

## Chapter 1

### Introduction

#### 1.1 Wireless Transceivers and Filtering

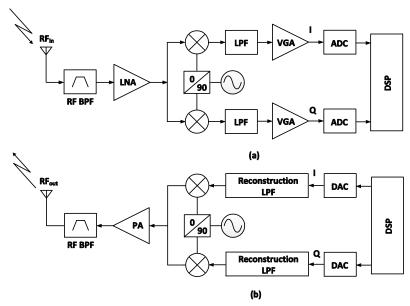

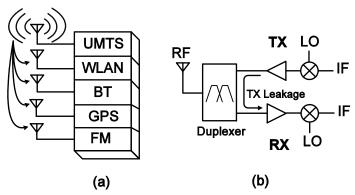

Wireless communication systems play a significant role in our daily life and many people recognize acronyms like GSM, WiFi/WLAN, Bluetooth and GPS. To fulfill the increasing demands for higher data rates and to cope with the plethora of existing and new applications, continuous innovations in wireless technology are wanted. Moreover, the tremendous growth of wireless communication combined with scarcely available spectrum asks for new, more programmable radio hardware. As will be discussed in section 1.2, this has led to the concept of a cognitive radio capable of smart Dynamic Spectrum Access (DSA). This asks for software-defined radio (SDR) hardware. In this thesis we will focus on programmable on-chip RF filtering for wireless applications. To understand the role of RF filtering, a typical zero-IF receiver and transmitter architecture which is suitable for CMOS integration is illustrated in Fig. 1.1. The received signal at the antenna is usually bandpassfiltered by an RF filter before applying it to a low noise amplifier (LNA). Typically this RF filter selects the band of desired signals, e.g. the GSM900 or GSM1800 band, or the Bluetooth 2.4 GHz band. The amplified signal at the output of the LNA is downconverted to baseband frequencies where it is lowpass filtered (LPF).

Figure 1.1. Zero-IF (a) Receiver (b) Transmitter architecture.

A variable gain amplifier (VGA) further amplifies the signal to fit to the dynamic range of the analog to digital converter (ADC). The rest of the processing is typically performed in the digital domain. Low-cost integration of tremendous amounts of digital signal processing (DSP) plays a crucial role in favoring CMOS IC-technology.

At the transmitter side the digital outputs are converted to an analog signal via a pair of Digital to Analog Converters (DAC). After filtering, frequency mixers upconvert the baseband signal to RF frequencies. A power amplifier (PA) amplifies the signal and after proper filtering to satisfy the transmission mask requirements the output signal is delivered to the antenna.

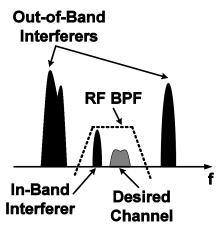

As indicated in Fig. 1.2, the received input signal at the antenna not only encompasses the desired channel to be received, but also interferers<sup>1</sup>. For in-band interferers obeying the same communication standard, e.g. a neighbor channel, the strength of the interference is limited, as defined by a radio standard. However, out-of-band blockers from other wireless networks may also exist, and can be much stronger (e.g. a TV transmitter delivering several kW).

-

<sup>&</sup>lt;sup>1</sup> In this thesis we will apply "interfering" and "blocking" signals within the same meaning.

Figure 1.2. Typical received signal at the antenna.

If the interfering signals hit the LNA and other blocks in the receiver chain without proper filtering, the limited linearity and dynamic range of these blocks will deteriorate the signal to distortion ratio. If the intermodulation or cross-modulation distortion falls in the desired band, it degrades the sensitivity of the receiver, i.e. reliable reception is no longer guaranteed. In the case of high-power interferers the receiver might even be overloaded due to the limited compression point ( $P_{1dB}$ ) of the receiver, which results in reduced amplification of the desired signal and consequently a further reduced signal to distortion ratio. To avoid these issues, the RF pre-filter should provide a proper rejection for out-of-band blockers without significantly affecting the in-band distortion level and noise figure (NF) of the receiver. Note that the insertion loss of the filter in the pass-band deteriorates the NF with the same amount.

RF filters based on surface acoustic wave (SAW) or bulk acoustic wave (BAW) resonators are widely used in wireless communications. These filters offer small feature size, high quality factor (Q), temperature stability and good power handling capability. However, they are mostly applied as off-chip components which adds to size and cost of the wireless devices. The thin-film nature of BAW filters and applying piezoelectric materials such as aluminum nitride, which is compatible with CMOS integration, provides a possibility to integrate these filters on top of the integrated RF transceiver to avoid external components [1]. However, this needs extra process steps compared to a conventional CMOS technology, which adds cost and yield issues. Moreover there are technological challenges such as limited

uniformity of piezoelectric layer which directly translates to the variation of the center frequency of the filter [2, 3].

In single standard traditional receivers it is quite common and also cost-effective to apply an external SAW/BAW filter to suppress out of band blockers. However in dynamic spectrum access (DSA) applications, where the desired received frequency band varies (e.g. 50 MHz-6 GHz) with location and time, a flexibly programmable RF filtering is wanted, and acoustic wave filters cannot offer this. Implementing a low-cost, on-chip tracking filter in this regard is strongly wanted for DSA applications.

In the following sections a brief introduction on DSA ideas is given. The aim is to illustrate the significance and necessity of the re-configurability of the RF pre-filtering in the up-coming generation of the wireless transceivers. Later on the possibilities of on-chip and off-chip tunable RF filtering will be discussed.

#### 1.2 Tunable Filter Application Perspectives

#### 1.2.1 Multi-Band Multi-Standard Transceivers

The tremendous growth of wireless communication systems in recent years resulted in many wireless standards. Nowadays a single handheld device might cover quad-band GSM-EDGE (850, 900, 1800, 1900 MHz) and W-CDMA/HSPA (850, 900, 1900, 2100 MHz) cellular networks. Moreover, a smartphone usually supports Wi-Fi connectivity at 2.4 and 5.8 GHz, and Bluetooth and GPS as well. Consideration of size, cost and battery lifetime have motivated the idea of sharing the hardware of the transceivers as much as possible in a single chip, leading to multi-band multi-standard transceivers. In order to receive multiple bands with a single RF front-end, a tunable filter or a bank of switchable filters is required. For a limited number of frequency bands a filter bank might be a practical option [4]. When increasing the number of frequency bands, the switchable filter bank concept increasingly becomes less practical. Tunable filtering is highly wanted in this regard.

### 1.2.2 Software Radio and Software-Defined Radio

Unlike digital signal processing circuitry in Fig. 1.1, the analog front-end hardware in many respects is not scaling favorably with new CMOS technologies.

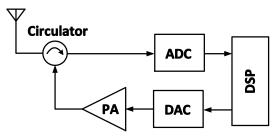

Figure 1.3. Software radio (SWR) architecture proposed by Mitola [5].

Even achieving the same linearity and dynamic range performance is problematic in newer technologies due to the reduced supply voltage and increased impact of short channel effects. Moreover, analog blocks at the receiver front-end are usually optimized for a specific application and adding flexibility and re-configurability to these blocks is difficult. These observations motivate attempts to minimize the amount of analog front-end hardware and push the digital part as close as possible to the antenna. The concept of a software radio (SWR) introduced by Mitola [5, 6] in the 90's, fits to this hardware trend. The SWR that Mitola envisioned is illustrated in Fig. 1.3.

In the architecture proposed by Mitola the received signal is directly digitized at RF by an RF ADC and fed to the DSP. At the transmitter the output of the RF DAC is amplified and transmitted via an antenna. The circulator routes the signals from the transmitter to the antenna and the received signals from antenna to the receiver without allowing the transmitted signals pass to the receiver. With the flexibility of the programming of the digital platform the SWR theoretically can receive any frequency band, with any modulation type and channel bandwidth. It might be even capable of receiving more than a single channel or wireless standard concurrently. The UK Defense Evaluation and Research Agency implemented a prototype of a SWR receiver for the 3-30 MHz HF band [7] in 2000. Still, the idea of SWR remains impractical so far for frequencies higher than UHF bands (30-300 MHz), especially due to the tough requirements on the ADC specifications. As high sample rate and high dynamic range is wanted simultaneously, power consumption estimates for an ADC covering the 1-6 GHz mobile bands can easily amount to about 1 kW [8]!

To reduce ADC requirements to what is feasible with state of the art CMOS ADCs, downconversion and filtering remains indispensable. The so-called Software-defined Radio (SDR) concept addresses this need, while still benefiting from digital flexibility. The SDR front-end architecture closely follows Fig. 1.1, but now with

sufficient bandwidth and/or re-configurability to receive RF signals in different frequency bands.

The RF pre-filtering which is required for SDR needs to be tunable to satisfy the multi-band reception property of a SDR. Although reconfigurable baseband filtering, for instance based on the switched-capacitor techniques discussed in [9], help to relax RF filter requirements, tunable RF pre-filtering is still required to suppress strong out-of-band blockers.

#### 1.2.3 Cognitive Radio

In the traditional spectrum allocation regulations, almost all spectrum allocated for mobile radio communications, is regulated on a primary basis: dedicated to specific and exclusive use. However, this spectrum allocation is far from efficient, while there is a tremendously increasing demand for frequency spectrum. Although most parts of the spectrum below 6 GHz are allocated for specific use, spectrum measurement studies [10-12] show that most of the spectrum, in most of the places, most of the time remains unused. To increase efficiency, more liberal spectrum use has been advocated, based on knowledge of actual instantaneous local spectrum use. Such spectrum use is often referred to as Dynamic Spectrum Access or Opportunistic Spectrum Access. The term cognitive radio is also, loosely used, although dynamic spectrum access is just one possible aspect of cognitive radio as proposed in [13].

In this thesis we will use the term cognitive radio for a device with radio hardware and software, able to be aware of its operational environment so that it can dynamically and autonomously adjust its radio operating parameters. These parameters might include the modulation scheme, carrier frequency, bandwidth, transmitted power etc. The environment awareness might be provided by spectrum sensing [14, 15] available on-board and/or through geolocation database information. A comprehensive review of cognitive radio technology is presented in [16]. Similar to SDR, dynamic frequency band reception requires highly reconfigurable RF pre-filtering.

Although cognitive radio is a general concept, recently research attention is mostly focused on the application of cognitive radio in TV bands. In the United States the Federal Communications Commission (FCC) proposed to construct new rulemaking in 2000, to offer possibilities for secondary spectrum use [17]. The idea is that secondary unlicensed (secondary) users will utilize the spectrum when it is

not used by users with a primary license. If a the licensed primary user starts communication, the secondary user should stop working or change its frequency band. In later reports [18-20] the FCC specified the regulations for fixed and portable devices operating in unlicensed TV white spaces (TVWS). Apart from mostly unused spectrum availability in VHF and UHF bands (54-698 MHz) which are applied for full service TV stations, this frequency range is also very suitable for wireless communication in terms of propagation characteristics such as path loss. Possible applications of TV white spaces include rural broadband access, new WiFilike devices for increased broadband connectivity, machine-to-machine (M2M) applications and new mobile network operator deployments.

Utilization of TVWS frequency bands for cognitive radio applications also gained attention in term of international standardizations. For instance IEEE 802.22 [21] aims at wireless regional area networks (WRAN) providing broadband access in rural areas utilizing TV white spaces. IEEE 802.11af is another example aiming at Wi-Fi like networks also called White-Fi [22].

As dynamic spectrum access is first allowed for TVWS frequency bands, and as path loss is attractive in those bands, the filter designs proposed in this thesis are aiming at TVWS frequencies, aiming to cover the entire TV-spectrum.

#### 1.3 RF Pre-Filtering for Dynamic Spectrum Access

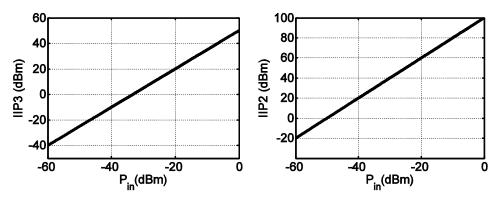

As discussed earlier the desired band for DSA might vary over location and time. The interference caused by other licensed or unlicensed networks will then also vary, leading to variable distortion levels for different frequency bands [23]. RF pre-filtering is an indispensable requirement for reliable communication also for DSA. Consider a simple example where two single-tone interfering signals are generating intermodulation terms in the desired band due to nonlinearity of the front-end. If we assume the required IIP2 and IIP3 is such that the noise floor (N) of the receiver in the received channel is equal to the distortion level, then the required IIP3 and IIP2 for the front-end will be as following:

$$IIP3 = \frac{3}{2}P_{in} - \frac{1}{2}N\tag{1.1}$$

$$IIP2 = 2P_{in} - N \tag{1.2}$$

Figure 1.4. Required IIP2 and IIP3 for an RF front-end to bring IM2 and IM3 below a -100 dBm noise floor, assuming two blockers with each P<sub>in</sub>.

In (1.1) and (1.2) all values are in dBm. Assuming 10 MHz channel bandwidth and 4 dB noise figure, a -100 dBm noise floor (N) results, and applying equations (1.1) and (1.2) the required IIP3 and IIP2 is illustrated in Fig. 1.4.

At the antenna, blocking signals up to 0 dBm are not unlikely, and the GSM and Bluetooth standards for instance specify blocker levels up to 0 dBm. Without pre-filtering, this would require an IIP3 of around 50 dBm and IIP2 of 100 dBm which are impractical to be achieved with the current CMOS technologies. Second order nonlinearity of the receiver front-end at RF frequencies produces sum and difference terms which might be removed by an octave bandwidth BPF [24]. Also, differential architectures for the receiver front-end building blocks can improve the even-order nonlinearity significantly. However, the odd higher order intermodulation terms and also the cross modulation from various interfering signals might fall in the desired band.

In a real situation more than just two blocking signals might hit the receiver front-end. In [25], 3<sup>rd</sup> order linearity requirements are derived in case of multiple tones or OFDM signals, considering both IM3 but also cross-modulation effects. Calculations for different scenarios show that often the amount of required linearity is not achievable with state of the art CMOS receivers without proper RF pre-filtering. Note that a filter would also have to satisfy such linearity requirements. Only if a filter can have better linearity and/or compression point than a receiver front-end, there is something to be gained. This is the aim of the current thesis.

It is not easy to quantify how much benefit DSA can bring, as it depends on many factors amongst which spectrum statistics. Marshall claims in an RFIC 2012

workshop that a factor of 10 improvement in aggregate communication throughput can practically be realized using DSA. He has shown that the use of tunable filters can significantly reduce the probability of receiver overload as well as the intermodulation induced noise floor in receivers, which can relax receiver IIP3 requirements easily by >20 dB [24, 26]. In an inspection based on a spectrum density mitigation algorithm called "Pick Quietest Band First" [24], it was shown that for a fixed receiver with IIP3 of -5 dBm and a pre-filter bandwidth of 20%, the noncognitive radio has a 4 percent probability of overload, while the equivalent cognitive radio would have  $10^{-7}$ . Moreover the statistical approach in [24] also illustrates that the most important resource to avoid front end overload in a cognitive radio is the filter. Increasing IIP3 also helps but is much less significant in reducing the probability that a given node will be overloaded.

#### 1.4 RF Tunable Filtering Possibilities

Filters have a long history and countless options to realize filters exist. Here we mention somewhat arbitrarily a few options to realize tunable filtering. In [27, 28] tunable off-chip electromagnetic and cavity band-pass filters are discussed. These filters can have low insertion loss and remarkable out-of-band rejection with large power handling capabilities but their large size usually is not suitable for mobile handheld devices.

Electro-statically actuated MEMS resonators have also been proposed as CMOS compatible tunable bandpass filters [29, 30]. However, their high motional impedance level which might be at least several kOhms, limits their application in a 50  $\Omega$  environment at GHz frequencies, even though attempts are made to reduce this impedance [31]. With a high impedance level, power matching in 50  $\Omega$  systems will require LC matching networks which are usually narrow-band and to be avoided in the integrated circuits. Moreover, a high impedance level leads to large voltage swings that might cause significant distortion due to the nonlinearity of the electro-statistical resonators [32].

In acoustic wave filters (SAW/BAW) the resonance frequency is defined by the piezoelectric material dimensions and its properties. Currently the piezoelectric effect is not strong enough to change the center frequency significantly.

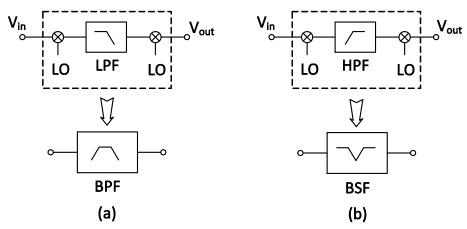

Figure 1.5. Frequency translated filtering (a) a lowpass filter is translated into a bandpass filter (b) a highpass filter is translated into a bandstop or notch filter.

For instance for BAW filters typically the frequency change is less than 20 ppm/V [33] which means 0.2% variation at the resonance frequency even if we apply a DC voltage of 100V. There is an active research community proposing new materials and implementation techniques, however widely tunable acoustic wave filters are not yet available [34]. There have also been efforts to implement tunable filters with fixed resonators (e.g. BAW/SAW) and tunable capacitors [35]. The tuning range of these filters is very small and usually these techniques are used to compensate the variations of the center frequency posed by the process [36].

In this thesis we are looking for tunable on-chip filtering solutions. On-chip LC filters with variable capacitors are usually suffering from losses of on-chip inductors. Q-Enhancing techniques apply on chip low Q inductors in combination with an active negative impedance to compensate for resistive losses in the inductors. These filters have a limited dynamic range restricting their usefulness as RF pre-filters. RF active filters provide high Q and tunability. However, the linearity and noise of these filters are not good enough to be used as RF pre-filtering block after the antenna [37, 38].

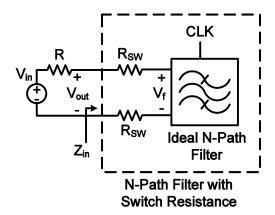

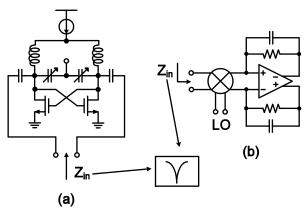

To implement on-chip RF pre-filtering, a technique referred to as frequency-translated filtering is gaining strong interest in recent years. The concept is illustrated in Fig. 1.5. The input signal at RF frequencies is downconverted before applying it to a lowpass or highpass filter (LPF/HPF). The filter output signals are upconverted again to RF. Overall, a bandpass or bandstop filter at RF frequencies is emulated. The baseband filters might be as simple as an RC network and frequency

mixers can be implemented with hard driven CMOS switches. As the bandwidth of the baseband filter can be much lower than the RF center frequency (=switching frequency), the resulting Q of the RF bandpass filter can be high. As an example, a 5 MHz baseband frequency and a 1 GHz switching frequency would result in a Q of 100, which is an order of magnitude higher than feasible with CMOS LC-filters. Moreover the center frequency is digitally tunable with the clock frequency.

The architecture shown in Fig. 1.5 is usually not implemented with one mixer-filter-mixer signal-path, but usually with multiple paths, driven by multiphase clocks. This is the reason that these kind of filters are also addressed as "N-Path filters" in literature. Although the concept of filtering based on passive mixers was developed bottom-up during research in the IC Design Group, we discovered later that the idea has much older roots. A brief history of the N-path filtering is discussed in the next section.

#### 1.5 Frequency Translated N-Path Filtering

N-path filtering in the electronic domain received considerable attention in the 60's [39, 40] as a continuous-time filtering technique at kHz-range frequencies. There is even older work on electro-mechanical implementations, in which a mechanical motor drives rotating switches to implement the multi-phase clocking, with RC filters to realize the baseband filter (the term "commutating filters" is sometimes also used).

Fig. 1.6 shows two cascaded 4-path filtering stages which are used to realize a bandpass filter at 108 kHz center frequency [40]. The switches are implemented by solid state diodes and capacitors with off-the-shelf components. In chapter 2, detailed analysis will show that the switches in Fig 1.6 are in fact realizing a multiphase passive mixer which translates the lowpass characteristic of the RC network to create a bandpass behavior around the switching frequency.

Later there have been attempts to apply N-path networks to implement higher order filtering. In [41], two 3-path RC resonators have been replaced in an active RC lowpass filter to realize a bandpass filter with two complex pairs of poles. In [42], the LC resonators in a coupled resonator LC bandpass filter prototype for a center frequency of 5.8 kHz are replaced by N-path switched-RC networks to implement a higher order N-path bandpass filter.

Figure 1.6. Two stage cascaded 4-path filter [40].

N-path filters have been applied with gyrators as well. In an LC low pass filter prototype the inductor might be replaced by a gyrator and capacitor. If the capacitors are replaced by N-path switched-RC networks then the lowpass characteristic can be transferred to a bandpass one [43].

The N-path filters discussed so far are time-variant circuits that produce a continuous-time output. In the 80s, the N-path technique has also been adopted in discrete-time switched-capacitor filters [44-46]. Instead of simple switched RC networks in each path, more complex blocks including operational amplifiers have been applied to realize higher order switched-capacitor N-path filters. The mismatch between different paths can deteriorate the filter functionality. To mitigate path mismatch effects, Fettweis and Wupper introduced the concept of pseudo-N-path filters [47]. In these filters there is actually only one physical path in which the sampled data is transferred to different capacitors via an analog shift register. Another problem of N-path filters is the frequency selectivity around the harmonics of the switching frequency. In [48] a passive approach with just switches and capacitors is presented to suppress harmonic selectivity at the even harmonics of a single-ended N-path filter. Normally the even harmonics might be rejected via a differential architecture. To increase the filter order avoiding the active components, an all passive switched-capacitor discrete-time domain approach is developed in [44] in which just capacitors and switches are applied.

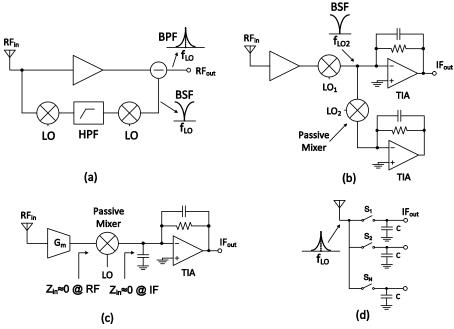

In recent years continuous-time frequency-translated filtering has been explored in different forms to realize RF filtering in receiver. Some examples are shown in Fig. 1.7. In [49] a frequency-translated notch filter is applied in the lower feedforward path of Fig. 1.7.a, and its output signal is subtracted from the output of the main amplifier path. Overall, this realizes a bandpass filter around the mixing frequency at the output of the gain block.

Figure 1.7. Frequency translated filtering (a) Translational loop [49]. (b) BSF or notch filter at IF frequencies [50]. (c) Highly linear receiver [51]. (d) Mixer first receiver [52], [53], [54].

Another example of frequency translated filtering is shown in Fig. 1.7.b, where the virtual ground impedance of a Trans-Impedance Amplifier (TIA) at baseband is transferred around  $f_{LO2}$ . As the virtual ground impedance increases with baseband frequency, overall a notch filter results that can suppress blockers [50].

Another way to exploit the low virtual ground impedance is shown in Fig. 1.7.c [51]. Here, the low input impedance of the TIA is transferred around the LO frequency by a passive mixer to limit the voltage swing at the output of the input transconductance (G<sub>m</sub>) block. In this way voltage gain at RF is low which is beneficial for linearity in general [55], but even more for nanometer CMOS devices in which large drain voltage swings strongly degrade linearity [51]. Note that, in contrast to Fig. 1.7.b, a wideband low virtual ground impedance is required, which is one of the reasons why a shunt capacitor to ground is added at the virtual ground node. A different class of receivers completely omits an LNA and directly put the mixer at the antenna [52-54]. An example of such a "mixer-first" receivers is shown in Fig. 1.7.d with a capacitive termination [54].

Figure 1.8. Application of N-path filtering in the receiver front-end [56].

If we consider the antenna as a source with resistance, this circuit actually is the switched-RC N-path bandpass filter used in Fig. 1.6, if the output is taken at the antenna node. Instead of a capacitor only, often also a TIA with RC load is used [53], which allows for realizing impedance matching. In recent years and especially during the period of the research project which led to this thesis some applications of the switched-RC N-path filters were presented in literature [57-59]. For instance as indicated in Fig. 1.8, two 4-path switched-RC filters are connected to the gate and drain of the input NMOS transistors providing bandpass filtering around f<sub>LO</sub>. Moreover the RC-filtering at the input of TIA is also upconverted to RF frequencies via passive mixers realizing bandpass filtering at the output of LNA. In [58] N-path filters are applied to provide image rejection in a super-heterodyne receiver.

As mentioned earlier the zero-IF voltage outputs on the baseband capacitors shown in Fig. 1.7.d undergo a frequency filter similar to the RF node before the switches and even better because switch resistance doesn't limit achievable filter attenuation. Then the question may arise, what is the benefit of applying RF node filtering instead of exploiting the readily available baseband signals? We found the following benefits:

- Compared to receivers starting with an LNA or Low Noise Trans-Conductance Amplifier (LNTA), out-of-band linearity and compression point can be significantly higher, making it sensible to use an N-path filter in front of such receivers.

- 2. With the application of N-path filters in front of LNA or even embedded in LNA as Broadcom proposed in [56] (see Fig. 1.8), compared to other mixer-

first receivers, the linearity becomes similar, but 1/f noise is better. This is because typically voltage gain is required at RF before downconversion, to reduce the Flicker noise of IF amplifiers sufficiently. Note that a mixer-first I/Q architecture requires 4 baseband low-noise amplifiers at baseband with low 1/f noise, while one LNA without 1/f noise requirements suffices at RF. This typically renders a significant power dissipation advantage.

#### 1.6 Research Objectives

This thesis focusses on N-path filters for RF frequencies. Most traditional analog building blocks suffer from the lower supply voltage headroom and short-channel effects of downscaled CMOS technologies. However in new CMOS technologies, MOS switches with low on-resistance and with less parasitic capacitances are available. Also capacitors with high quality factors can be realized, exploiting the many metal layers. Some processes even have high density capacitor realized via a thin oxide between two metal layers (so called "MIM capacitors"). These passive components are very linear and can hence be an attractive basis for high linearity programmable filters to improve the performance of receiver front-ends in new CMOS technologies.

The N-path filtering concept provides high-Q filtering with just switches and capacitors without any inductors. Despite of the fact that the N-path filters were well known in the 60s, their application to RF frequencies has not been considered until recently. This thesis aims to show that such filters can have excellent tunability, high linearity and compression point and low noise in modern CMOS technologies. We will aim at tunable high-Q filters for DSA applications in the TV bands. In this thesis we are aiming to provide closed form equations to model N-path switched-RC filters and demonstrate these filters through CMOS prototypes. Both N-path bandpass and bandstop (notch) filters will be discussed. Moreover the N-path filtering will be applied to provide spatial filtering in a 4-element phased-array system.

The switched-RC N-path filters are in fact Linear Periodically Time Variant (LPTV) systems. Since the 60's several analysis methods have been developed based on the time-varying transfer function introduced by Zadeh [60] for N-path filters in the context of LPTV systems. An approximate analysis just for the main side band of N-path filters in the form of commutated capacitors as seen in Fig. 1.6 was presented in [39]. More accurate analysis approaches are presented in [61, 62]. However none

of these works properly describe the frequency aliasing issues associated with N-path filters.

More recently, analysis results have also been presented by Andrews [63] and Mirzaei [64]. In their approximate approaches the RF impedance seen by the N-path filter might include also reactive components. However, the analysis presented here is more comprehensive for the switched-RC case, covering all frequencies and mixing side-bands. Moreover, unlike previous works the equations are valid for all RC values. In this thesis we will assume that the RF impedance seen by the N-path network is purely resistive. Thus the general form of state-space analysis for LPTV networks presented in [65], leads to a single state one for the networks we are considering in this thesis [66]. One set of closed form equations for switched-RC N-path filters will be derived. Then the analysis results will be applied to describe filter properties including possible imperfections such as noise and harmonic mixing.

Here we will mostly work on the N-path filters in the context of a receiver. N-path filtering might also proof beneficial for transmitters or frequency synthesizers. Then the harmonic mixing and limited power handling might probably be limiting factors.

Most parts of this thesis are published in [67-71]. It is worth noting that some relevant aspects are not discussed in our work, partly because they are already addressed by other publications. For instance the phase noise and switch nonlinearity effect which is not discussed here, is covered in [64].

#### 1.7 Thesis Organization

The organization of this thesis is as follows:

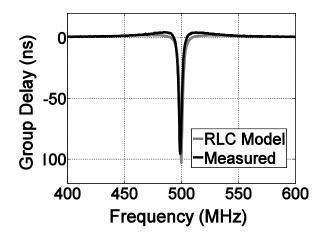

In chapter 2, an architecture for switched-RC differential N-path bandpass filters is discussed. An intuitive understanding of the operation of this N-path filter architecture leading to a mathematical modeling and exact analysis of the circuit is presented. Measurement of an implemented prototype of a differential 4-path filter in 65 nm CMOS technology is provided and compared with state of the art. The derived equations describing the properties of the N-path filters are in a general form, however the numerical examples are presented for the 4-path circuit implemented on-chip. An RLC tank circuit which provides a simple model around the switching frequency is derived for the N-path switched-RC networks.

In chapter 3, N-path notch filters are presented. Here both single ended and differential architectures are discussed. Just as for the N-path bandpass filters, a set

of closed-form equations describing the input-output desired and undesired transfers are derived. Moreover notch filters are also modeled as a simplified parallel RLC tank circuit around the notch frequency.

In chapter 4, the N-path technique is applied to implement a 4-element phased-array system. The Spatial- and frequency domain filtering is provided at the antenna inputs. This brings interference rejection for out-of-band/beam blockers already at the antenna inputs. A prototype is implemented and measurement results are compared with state of the art work presented in recent years.

Chapter 5 concludes the thesis, providing a summary of the key parameters of the implemented chips and general insights for the N-path filters and phased-array system discussed in preceding chapters.

#### 1.8 References

- [1] M. A. Dubois, *et al.*, "Monolithic above-IC resonator technology for integrated architectures in mobile and wireless communication," *Solid-State Circuits, IEEE Journal of*, vol. 41, pp. 7-16, 2006.

- [2] C. Lambert, et al., "BAW Devices: Technology Overview and Manufacturing Aspects," 2nd International Symposium on Acoustic Wave Devices for Future Mobile Communication Systems, March 2004.

- [3] F. Z. Bi and B. P. Barber, "Bulk acoustic wave RF technology," *Microwave Magazine, IEEE*, vol. 9, pp. 65-80, 2008.

- [4] R. Pullela, *et al.*, "An integrated closed-loop polar transmitter with saturation prevention and low-IF receiver for quad-band GPRS/EDGE," *IEEE ISSCC, Digest of Technical Papers*, pp. 112-113, 8-12 Feb. 2009.

- [5] J. Mitola, III, "Software radios-survey, critical evaluation and future directions," *Telesystems Conference*, NTC-92., National, pp. 13/15-13/23, 19-20 May 1992.

- [6] J. Mitola, III, "Software radios: Survey, critical evaluation and future directions," *Aerospace and Electronic Systems Magazine, IEEE*, vol. 8, pp. 25-36, 1993.

- [7] N. C. Davies, "A high performance HF software radio," *HF Radio Systems and Techniques, Eighth International Conference on (IEE Conf. Publ. No. 474)*, pp. 249-256, 2000.

- [8] E. A. M. Klumperink, *et al.*, "Cognitive radios for dynamic spectrum access polyphase multipath radio circuits for dynamic spectrum access," *Communications Magazine, IEEE*, vol. 45, pp. 104-112, 2007.

- [9] R. Bagheri, et al., "An 800MHz to 5GHz Software-Defined Radio Receiver in 90nm CMOS," IEEE ISSCC, Digest of Technical Papers, pp. 1932-1941, 6-9 Feb. 2006.

- [10] M. A. McHenry, et al., "Chicago spectrum occupancy measurements & analysis and a long-term studies proposal," *Proceedings of the first international workshop on Technology and policy for accessing spectrum,* Boston, Massachusetts, 2006.

- [11] M. A. McHenry and D. McCloskey, "Multi-band, multi-location spectrum occupancy measurements," *International Symposium on Advanced Radio Technologies, ISART*, Boulder, CO, USA, Mar. 2006.

- [12] "Spectrum Reports," Available: http://www.sharedspectrum.com/papers/spectrum-reports

- [13] J. Mitola, III and G. Q. Maguire, Jr., "Cognitive radio: making software radios more personal," *Personal Communications, IEEE*, vol. 6, pp. 13-18, 1999.

- [14] M. S. Oude Alink, *et al.*, "A 50MHz-To-1.5GHz Cross-Correlation CMOS Spectrum Analyzer for Cognitive Radio with 89dB SFDR in 1MHz RBW," *New Frontiers in Dynamic Spectrum, IEEE Symposium on*, pp. 1-6, April 2010.

- [15] M. S. Oude Alink, *et al.*, "A CMOS spectrum analyzer frontend for cognitive radio achieving +25dBm IIP3 and -169 dBm/Hz DANL," *Radio Frequency Integrated Circuits Symposium (RFIC), IEEE*, pp. 35-38, June 2012.

- [16] K. G. Shin, K. Hyoil, A. W. Min, and A. Kumar, "Cognitive radios for dynamic spectrum access: from concept to reality," *Wireless Communications, IEEE*, vol. 17, pp. 64-74, 2010.

- [17] FCC, "Notice of Proposed Rulemaking" ET Docket No. 00-402, Nov. 2000.

- [18] FCC, "Notic of Proposed Rulemaking," ET Docket No. 04-113, May 2004.

- [19] FCC, "Second Report and Order and Memorandum Opinion and Order," ET Docket No. 08-260, Nov. 2008.

- [20] FCC, "In the Matter of Unlicensed Operation in the TV Broadcast Bands Additional Spectrum for Unlicensed Devices Below 900MHz and in the 3GHz Band," Sep. 2010.

- [21] "IEEE 802.22 Working Group on Wireless Regional Area Networks," Available: http://www.ieee802.org/22/

- [22] R. Kennedy and P. Ecclesine, "IEEE P802.11af Tutorial," July 2010, Available: https://mentor.ieee.org/802.11/dcn/10/11-10-0742-00-0000-p802-11af-tutorial.ppt

- [23] O. Bendov, "Limits on Fixed Broadband Devices for Interference-Free Operation in the DTV Spectrum," *Broadcasting, IEEE Transactions on*, vol. 53, pp. 746-754, 2007.

- [24] P. F. Marshall, "Dynamic Spectrum Management of Front End Linearity and Dynamic Range," *New Frontiers in Dynamic Spectrum Access Networks, DySPAN, 3rd IEEE Symposium on*, pp. 1-12, 14-17 Oct. 2008.

- [25] D. H. Mahrof, E. A. M. Klumperink, J. C. Haartsen, and B. Nauta, "On the Effect of Spectral Location of Interferers on Linearity Requirements for Wideband Cognitive Radio Receivers," New Frontiers in Dynamic Spectrum, DySPAN, IEEE Symposium on, pp. 1-9, 6-9 April 2010.

- [26] P. F. Marshall, "Cognitive radio as a mechanism to manage front-end linearity and dynamic range," *Communications Magazine*, *IEEE*, vol. 47, pp. 81-87, 2009.

- [27] J. Uher and W. J. R. Hoefer, "Tunable microwave and millimeter-wave band-pass filters," *Microwave Theory and Techniques, IEEE Transactions on*, vol. 39, pp. 643-653, 1991.

- [28] I. Reines, et al., "1.6-2.4 GHz RF MEMS tunable 3-pole suspended combline filter," Microwave Symposium Digest, IEEE MTT-S International, pp. 133-136, 15-20 June 2008.

- [29] J. R. Clark, M. A. Abdelmoneum, and C. T. C. Nguyen, "UHF high-order radial-contour-mode disk resonators," *Frequency Control Symposium and PDA Exhibition Jointly with the 17th European Frequency and Time Forum*, pp. 802-809, 4-8 May 2003.

- [30] C. T. C. Nguyen, "Integrated Micromechanical Radio Front-Ends," VLSI Technology, Systems and Applications, VLSI-TSA, International Symposium on, pp. 3-4, 21-23 April 2008.

- [31] J. Dewdney, I. T. Wu, W. Mian, and W. Jing, "Reduction of impedance and feedthrough parasitics of RF micromechanical resonators," *Silicon Monolithic Integrated Circuits in RF Systems (SiRF), IEEE 11th Topical Meeting on*, pp. 165-168, 17-19 Jan. 2011.

- [32] V. Kaajakari, T. Mattila, A. Oja, and H. Seppa, "Nonlinear limits for single-crystal silicon microresonators," *Microelectromechanical Systems, Journal of*, vol. 13, pp. 715-724, 2004.

- [33] R. Aigner, H. Ngoc-Hoa, M. Handtmann, and S. Marksteiner, "Behavior of BAW devices at high power levels," *Microwave Symposium Digest, IEEE MTT-S International*, pp. 429-432, 12-17 June 2005.

- [34] R. Aigner, "Tunable acoustic RF-filters: Discussion of requirements and potential physical embodiments," *European Microwave Conference* (*EuMC*), pp. 787-790, 28-30 Sept. 2010.

- [35] K. Hashimoto, S. Tanaka, and M. Esashi, "Tunable RF SAW/BAW filters: Dream or reality?," Frequency Control and the European Frequency and Time Forum (FCS), Joint Conference of the IEEE International, pp. 1-8, 2-5 May 2011.

- [36] C. Tilhac, et al., "A tunable bandpass BAW-filter architecture using negative capacitance circuitry," Radio Frequency Integrated Circuits Symposium (RFIC), IEEE, pp. 605-608, June 2008.

- [37] W. B. Kuhn, D. Nobbe, D. Kelly, and A. W. Orsborn, "Dynamic range performance of on-chip RF bandpass filters," *Circuits and Systems II: Analog and Digital Signal Processing, IEEE Transactions on*, vol. 50, pp. 685-694, 2003.

- [38] H. Xin and W. B. Kuhn, "A 2.5-GHz low-power, high dynamic range, self-tuned Q-enhanced LC filter in SOI," *Solid-State Circuits, IEEE Journal of*, vol. 40, pp. 1618-1628, 2005.

- [39] L. E. Franks and I. W. Sandberg, "An Alternative Approach to the Realization of Network Transfer Functions: The N-Path Filters," *Bell Sys. Tech. J.*, vol. 39, pp. 1321-1350, Sep. 1960.

- [40] L. Franks and F. Witt, "Solid-state sampled-data bandpass filters," *IEEE ISSCC, Digest of Technical Papers*, pp. 70-71, Feb. 1960.

- [41] E. Langer, "A new type of N-path N filters with two pairs of complex poles," *IEEE ISSCC, Digest of Technical Papers*, pp. 26-27, Feb. 1968.

- [42] G. Martinelli and M. Salerno, "Commutated capacitor bank as a filter resonator," *Electronics Letters*, vol. 14, pp. 427-428, 1978.

- [43] W. Heinlein, K. Moehrmann, and W. Holmes, "Double-tuned N-path bandpass filters using a single gyrator," *Circuit Theory, IEEE Transactions on*, vol. 18, pp. 728-729, 1971.

- [44] M. Ghaderi, J. Nossek, and G. Temes, "Narrow-band switched-capacitor bandpass filters," *Circuits and Systems, IEEE Transactions on*, vol. 29, pp. 557-572, 1982.

- [45] U. Kleine, et al., "An integrated six-path wave-SC filter," Solid-State Circuits, IEEE Journal of, vol. 20, pp. 632-640, 1985.

- [46] D. C. von Grunigen, *et al.*, "An integrated CMOS switched-capacitor bandpass filter based on N-path and frequency-sampling principles," *Solid-State Circuits, IEEE Journal of*, vol. 18, pp. 753-761, 1983.

- [47] A. Fettweis and H. Wupper, "A solution to the balancing problem in N-path filters," *Circuit Theory, IEEE Transactions on,* vol. 18, pp. 403-405, 1971.

- [48] S. M. Faruque, "Switched-capacitor FIR cell for N-path filters," *Electronics Letters*, vol. 18, pp. 431-432, 1982.

- [49] H. Darabi, "A Blocker Filtering Technique for SAW-Less Wireless Receivers," *Solid-State Circuits, IEEE Journal of*, vol. 42, pp. 2766-2773, 2007.

- [50] H. Khatri, P. S. Gudem, and L. E. Larson, "An Active Transmitter Leakage Suppression Technique for CMOS SAW-Less CDMA Receivers," *Solid-State Circuits, IEEE Journal of*, vol. 45, pp. 1590-1601, 2010.

- [51] Z. Ru, E. A. M. Klumperink, G. Wienk, and B. Nauta, "A software-defined radio receiver architecture robust to out-of-band interference," *IEEE ISSCC*, *Digest of Technical Papers* pp. 230-231, 8-12 Feb. 2009.

- [52] B. W. Cook, *et al.*, "Low-Power 2.4-GHz Transceiver With Passive RX Front-End and 400-mV Supply," *Solid-State Circuits, IEEE Journal of*, vol. 41, pp. 2757-2766, 2006.

- [53] C. Andrews and A. C. Molnar, "A Passive Mixer-First Receiver With Digitally Controlled and Widely Tunable RF Interface," *Solid-State Circuits, IEEE Journal of,* vol. 45, pp. 2696-2708, 2010.

- [54] M. Soer, et al., "A 0.2-to-2.0GHz 65nm CMOS receiver without LNA achieving >11dBm IIP3 and <6.5 dB NF," IEEE ISSCC, Digest of Technical Papers, pp. 222-223, 8-12 Feb. 2009.

- [55] S. C. Blaakmeer, E. A. M. Klumperink, D. M. W. Leenaerts, and B. Nauta, "The Blixer, a Wideband Balun-LNA-I/Q-Mixer Topology," *Solid-State Circuits, IEEE Journal of*, vol. 43, pp. 2706-2715, 2008.

- [56] A. Mirzaie, et al., "A 65nm CMOS quad-band SAW-less receiver for GSM/GPRS/EDGE," VLSI Circuits (VLSIC), IEEE Symposium on, pp. 179-180, 16-18 June 2010.

- [57] A. Mirzaei, et al., "A frequency translation technique for SAW-Less 3G receivers," VLSI Circuits, Symposium on, pp. 280-281, 16-18 June 2009.

- [58] A. Mirzaei, H. Darabi, and D. Murphy, "A Low-Power Process-Scalable Super-Heterodyne Receiver With Integrated High-Q Filters," *Solid-State Circuits, IEEE Journal of,* vol. 46, pp. 2920-2932, 2011.

- [59] M. Darvishi, R. van der Zee, E. A. M. Klumperink, and B. Nauta, "A 0.3-to-1.2GHz tunable 4th-order switched gm-C bandpass filter with 55dB ultimate rejection and out-of-band IIP3 of 29dBm," *IEEE ISSCC, Digest of Technical Papers*, pp. 358-360, 19-23 Feb. 2012.

- [60] L. A. Zadeh, "Frequency Analysis of Variable Networks," *Proceedings of the IRE*, vol. 38, pp. 291-299, 1950.

- [61] R. Fischl, "Analysis of a Commutated Network," *Aerospace and Navigational Electronics, IEEE Transactions on*, vol. ANE-10, pp. 114-123, 1963.

- [62] S. Yuh and I. Frisch, "A General Theory of Commutated Networks," *Circuit Theory, IEEE Transactions on*, vol. 16, pp. 502-508, 1969.

- [63] C. Andrews and A. C. Molnar, "Implications of Passive Mixer Transparency for Impedance Matching and Noise Figure in Passive Mixer-First Receivers," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol. 57, pp. 3092-3103, 2010.

- [64] A. Mirzaei and H. Darabi, "Analysis of Imperfections on Performance of 4-Phase Passive-Mixer-Based High-Q Bandpass Filters in SAW-Less Receivers," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol. 58, pp. 879-892, 2011.

- [65] T. Strom and S. Signell, "Analysis of periodically switched linear circuits," *Circuits and Systems, IEEE Transactions on*, vol. 24, pp. 531-541, 1977.

- [66] M. C. M. Soer, et al., "Unified Frequency-Domain Analysis of Switched-Series-RC Passive Mixers and Samplers," *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol. 57, pp. 2618-2631, 2010.

- [67] A. Ghaffari, E. A. M. Klumperink, and B. Nauta, "A differential 4-path highly linear widely tunable on-chip band-pass filter," *Radio Frequency Integrated Circuits Symposium (RFIC), IEEE*, pp. 299-302, 23-25 May 2010.

- [68] A. Ghaffari, E. A. M. Klumperink, M. C. M. Soer, and B. Nauta, "Tunable High-Q N-Path Band-Pass Filters: Modeling and Verification," *Solid-State Circuits*, *IEEE Journal of*, vol. 46, pp. 998-1010, May 2011.

- [69] A. Ghaffari, E. A. M. Klumperink, and B. Nauta, "8-Path tunable RF notch filters for blocker suppression," *IEEE ISSCC, Digest of Technical Papers*, pp. 76-78, Feb. 2012.

- [70] A. Ghaffari, E. A. M. Klumperink, and B. Nauta, "Tunable N-path notch filters for blocker suppression: modelling and verification," *Accepted to be Published in Solid-State Circuits, IEEE Journal of.*

- [71] A. Ghaffari, E. Klumperink, F. v. Vliet, and B. Nauta, "Simultaneous Spatial and Frequency Domain Filtering at the Antenna Inputs Achieving up to +10dBm Out-of-Band/Beam P<sub>1dB</sub> " *IEEE ISSCC, Digest of Technical Papers*, pp. 84-86, Feb. 2013.

## **Chapter 1. Introduction**

## Chapter 2

# **Tunable High-Q N-Path Bandpass Filters: Modeling and Verification**<sup>1</sup>

#### 2.1 Introduction

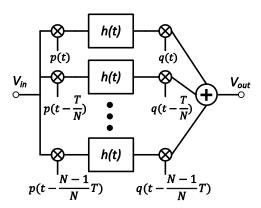

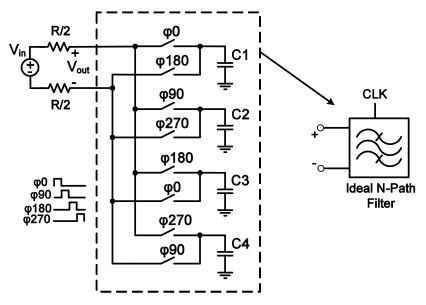

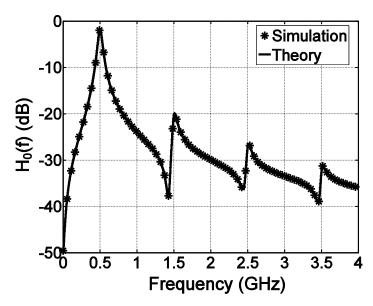

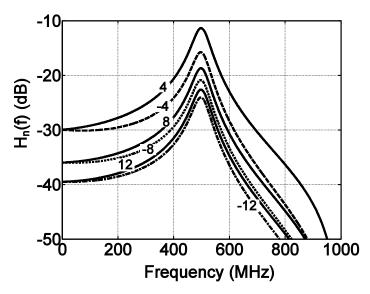

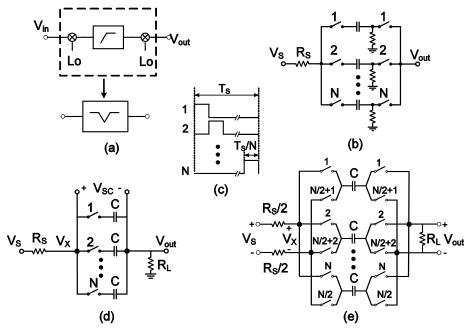

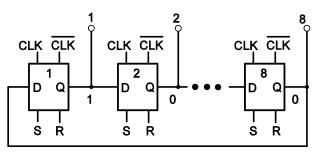

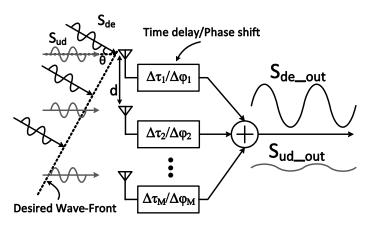

Inductor-less tunable filters based on periodically time variant networks have been addressed in literature under different names such as N-path filters, sampled data filters, commutated capacitors, etc. [1-7]. Discrete-time switched capacitor N-path filters are probably best known [4], but here we focus on their continuous-time predecessors. Fig. 2.1 shows a block diagram of an N-path filter composed of N identical Linear Time-Invariant (LTI) networks with impulse response h(t) and 2N frequency mixers (or modulators), driven by time/phase shifted versions of the clock p(t) and q(t). The time shift between two successive paths is T/N, where T is the period of the mixer clock. If the LTI networks exhibit a lowpass characteristic around DC, the mixing results in a band-pass around the mixing frequency.

<sup>&</sup>lt;sup>1</sup> This chapter has been published in the IEEE Journal of Solid-State Circuits:

A. Ghaffari, E. A. M. Klumperink, M. C. M. Soer, and B. Nauta, "Tunable High-Q N-Path Band-Pass Filters: Modeling and Verification," Solid-State Circuits, IEEE Journal of, vol. 46, pp. 998-1010, May 2011.

Figure 2.1. Architecture of an N-path filter [1] (p and q are the mixing functions and T is the period of the mixing frequency).

Simply put, the input signal is down-converted to baseband, filtered by the LTI network and then up-converted again to the original band of V<sub>in</sub>. The center frequency is determined by the mixing frequency, insensitive to filter component values. A high mixing frequency combined with a narrow low-pass filter bandwidth allows for a very high filter-Q.

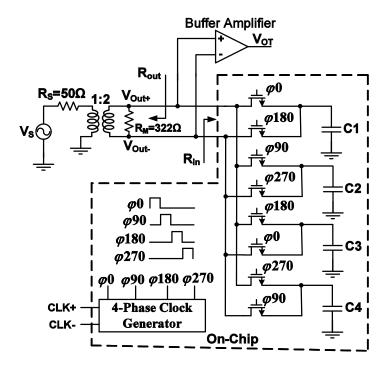

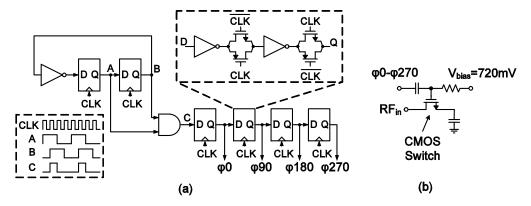

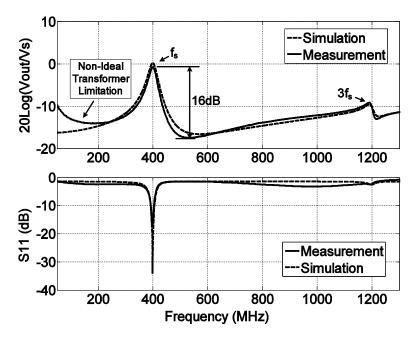

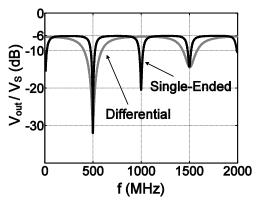

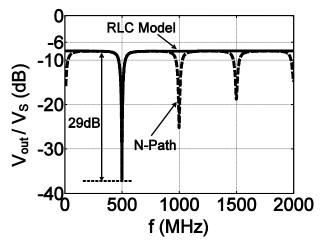

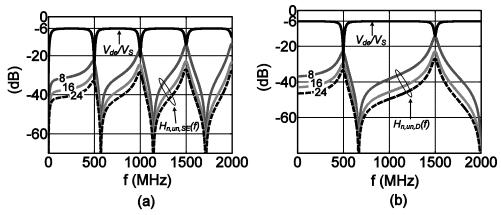

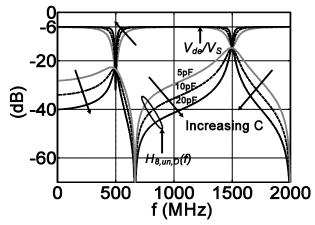

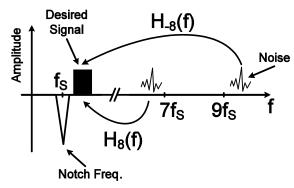

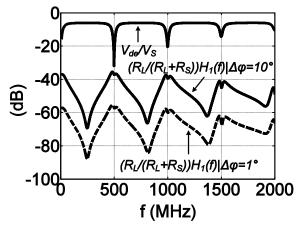

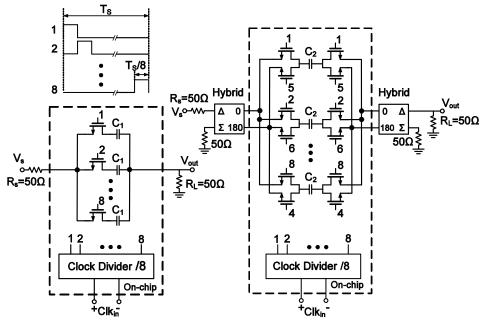

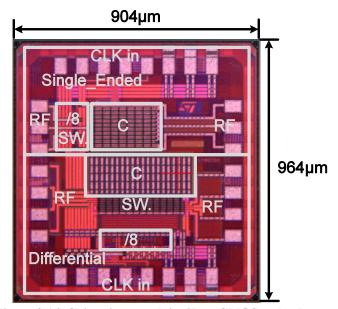

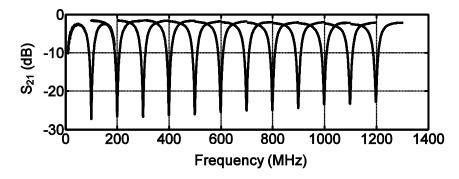

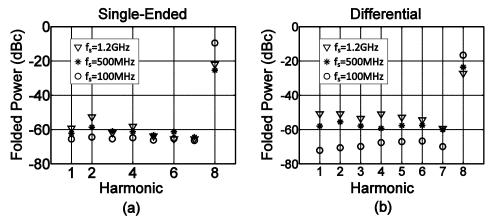

While time-continuous N-path filters have been proposed for kHz operating frequencies in the 60's [2], they seem to have been largely forgotten until recently. CMOS technology now allows N-path filters to work at TV-band RF frequencies [5, 6] and even above 1 GHz [7]. In [5] an 8-path single-ended structure is used, and in [6] we proposed a differential 4-path filter combined with a broadband off-chip transformer. In [7] the differential 4-path filters are applied in a quad-band SAW-less receiver. This chapter aims to model and verify N-path filter performance.

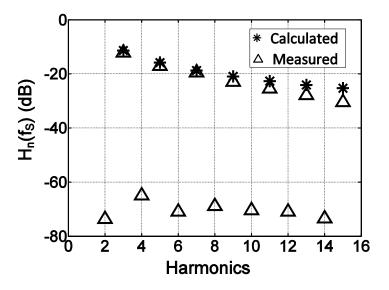

Using Linear Periodically Time-Variant (LPTV) analysis, exact expressions for the frequency response of differential N-path filters are derived. In [3] state-space analysis was used to derive the steady-state and transient response for a single-ended N-path filter, which is however not directly applicable to our differential architecture. We will derive one set of equations that characterizes filtering but also possible imperfections like harmonic folding, noise and the effects of the clock phase imbalance and mismatch. Moreover, an equivalent RLC tank circuit will be derived to approximate N-path filter behavior around the center frequency. Finally, we will verify the model via extended experimental results compared to [6].

In section 2.2 we will derive the differential N-path filter architecture starting from Fig. 2.1 and then analyze its transfer function in section 2.3. Section 2.4

presents basic characteristics of the differential N-path filter. Its chip implementation is discussed in section 2.5 and section 2.6 covers the measurement and verification versus the model.

#### 2.2 N-Path Bandpass Filter Concept

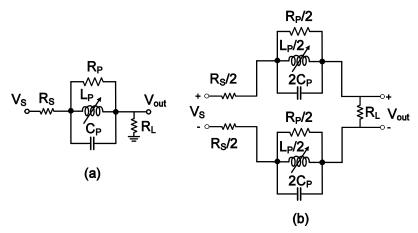

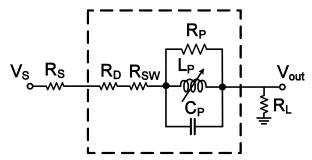

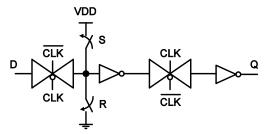

We will now derive the differential N-path filter from Fig. 2.1, where we aim for a high-linearity implementation using MOS switches as passive mixers, and RC lowpass filters (see Fig. 2.2.a). Furthermore we will try to develop some intuitive understanding of the filter behavior.

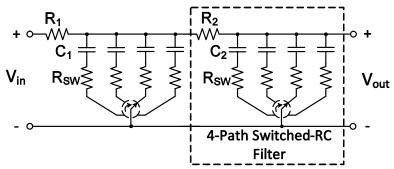

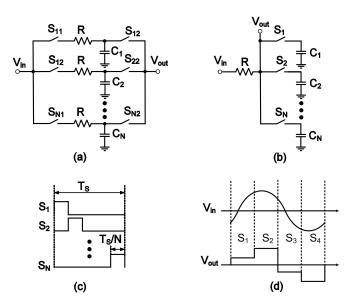

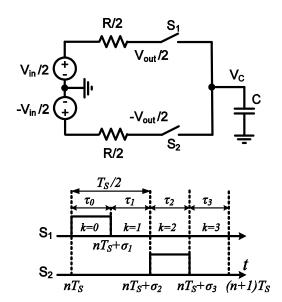

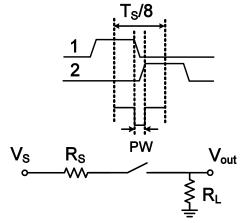

#### 2.2.1 Single-Ended Switched-RC N-Path Filter

Fig. 2.2.c shows a multiphase clocking scheme for the switches with non-overlapping on-times. Thus no charge exchange between capacitors can occur. For this reason and since a resistor is a memory-less element, it can be shared by all paths and shifted in front of them (Fig. 2.2.b). Moreover, if the clocks for the first and second set of switches are identical, the first set can also implement the function of the second set. V<sub>out</sub> becomes then available between the shared resistor and switches.

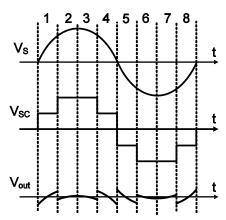

Fig. 2.2.b shows the resulting single-port single-ended N-path filter (V<sub>out</sub> is both input and output port). If we would use the capacitor voltages as outputs, the circuit behaves as a highly linear multiphase passive mixer [8, 9]. To intuitively understand the filter behavior of Fig. 2.2.b it is useful to model it as a two-step process: 1) the input signal experiences downconversion and lowpass filtering passing through the switches to the capacitors; 2) the same switches upconvert the filtered capacitor voltages to the output node. Another way to understand the filtering is to realize that at any moment one and only one capacitor is connected to the output node. If we assume that the time constant RC>>T<sub>N</sub>, the output voltage will be the average of the input voltage  $V_{in}$  over the time that the capacitor "looks at  $V_{in}$ ". If the frequency of V<sub>in</sub> is equal to the switching frequency, a particular capacitor will periodically observe the same part of the input waveform during every period. As each capacitor sees another part, the result is a staircase approximation of V<sub>in</sub>, see Fig. 2.2.d (4-path example). In fact, the capacitors experience a steady DC voltage and, in first order approximation, conduct no current. If the input frequency deviates from the clock frequency the signal portion seen by a capacitor will "travel over the period" and the capacitors experience an AC voltage (with  $f = \Delta f$ ).

Figure 2.2. (a) Switched-RC N-path filter. (b) Single-port, single-ended N-path filter. (c) Multiphase clocking. (d) Typical (in-band) input and output signal.

Thus the capacitors conduct current while switches are "on" and the average voltages on the capacitors become closer to zero. Consequently signals at input frequencies below or above the switching frequency will be suppressed with an amount depending on the offset from the switching frequency, on-time of the switch and RC time.

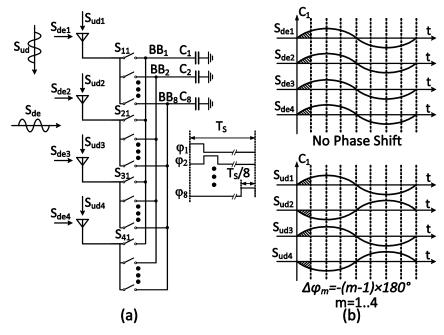

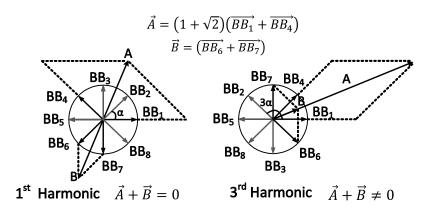

## 2.2.2 Differential Switched-RC N-Path Filter

If we repeat the analysis for input signals around the harmonics of the clock frequency, we also find non-zero average values. This fits to the comb-like characteristic of N-path filters [1], i.e. its repetitive selectivity around harmonics of the switching frequency. The differential architecture of Fig. 2.3 aims to cancel the even harmonic responses. Each path is differential-in and differential-out, but contains one grounded capacitor connected to two anti-phase driven switches. A 4-phase 25%-duty-cycle clock provides all required clocks (see Fig. 2.3). Now, for input signals around the even harmonics of the clock frequency, no net charge is stored on the capacitors in steady state and no upconverted signal appears at the output.

Figure 2.3. Single port differential 4-path filter.

#### 2.3 Analysis

To model the behavior of the N-path filter quantitatively, we will now apply LPTV state-space analysis [10, 11] to derive the exact shape of the transfer function of a differential N-path filter.

## 2.3.1 State-Space Analysis of LPTV circuits

For an LPTV network which is periodic with the frequency  $f_s = 1/T_s$ , the output spectrum is related to the input spectrum as [12]:

$$Y(f) = \sum_{-\infty}^{\infty} H_n(f)U(f - nf_s), \tag{2.1}$$

where  $U(f - nf_S)$  represents the shifted version of the input spectrum to account for frequency translation (mixing), while  $H_n(f)$  describes the spectral shaping (filtering) properties of an LPTV network. To simplify analysis, we make two assumptions: (1) The switches are ideal, i.e. their off-impedance is infinite and on-impedance is zero; (2) Switching occurs instantaneously.

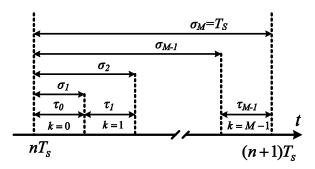

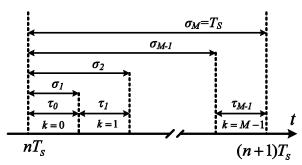

Figure 2.4. Time intervals for the state-space analysis.

The time interval  $nT_s < t < nT_s + T_s$  is divided into M portions (M is the number of the states) and each portion identified by k can be represented as  $nT_s + \sigma_k < t < nT_s + \sigma_{k+1}$ , k=0,..., M-1 and  $\sigma_0 = 0$  (see Fig. 2.4). During each interval there is no change in the state of the switches and the network turns to an LTI system. The state equations for interval "k" can be written as:

$$\dot{x}_k(t) = A_k x_k(t) + B_k u(t),

y(t) = C_k x_k(t) + D_k u(t),$$

(2.2)

where u(t) is the input vector,  $x_k(t)$  the state vector and y(t) the output vector. If we define  $u_k(t)$  and  $y_k(t)$  to be equal to the input u(t) and output y(t) respectively during the  $k^{th}$  interval, and zero otherwise, the state equations in (2.2) can be reformulated as [10, 11]:

$$\dot{x}_{k}(t) = A_{k}x_{k}(t) + B_{k}u_{k}(t)

+ \sum_{n=-\infty}^{\infty} (x_{k}(nT_{S} + \sigma_{k})\delta(t - nT_{S} - \sigma_{k}) - x_{k}(nT_{S} + \sigma_{k+1})\delta(t - nT_{S} - \sigma_{k+1})), \qquad (2.3)$$

$$y_{k}(t) = C_{k}x_{k}(t) + D_{k}u_{k}(t).$$

In (2.3) the Dirac's delta function  $\delta(t)$  has been used to add the effects of the initial conditions to the equations at the beginning of an interval, while subtracting it at the end of the interval. Then the output y(t) is the sum of all responses from M states in the system:

$$y(t) = \sum_{k=0}^{M-1} y_k(t). \tag{2.4}$$

Since we are interested in the spectrum of the output of the system we need to take the Fourier transform from (2.4). It can be shown [11] that if we apply a complex exponential  $u(t) = Ae^{j2\pi ft}$  as input, the output state at discrete moments can be calculated by reforming the state equations to a set of difference equations at the switching moments. Consequently the relation between the input and the output will be of the form:

$$x_k(nT_s + \sigma_k)\delta(t - nT_s - \sigma_k) = G_k(f)Ae^{j2\pi ft}\delta(t - nT_s - \sigma_k). \tag{2.5}$$

The input spectrum can be represented as a summation of sinusoidal signals. As a result the infinite summation in (2.3) takes the form:

$$\sum_{n=-\infty}^{\infty} (x_k (nT_s + \sigma_k)\delta(t - nT_s - \sigma_k) - x_k (nT_s + \sigma_{k+1})\delta(t - nT_s - \sigma_{k+1})) =$$

$$\left(\sum_{n=-\infty}^{\infty} (G_k(f)\delta(t - nT_s - \sigma_k) - G_{k+1}(f)\delta(t - nT_s - \sigma_{k+1}))\right) u(t).$$

(2.6)

By applying (2.6) to (2.3) and taking the Fourier transform, the spectrum of the state vector becomes:

$$X_{k}(f) = \sum_{n=-\infty}^{\infty} H_{n,k}(f)U(f - nf_{s}),$$

$$H_{n,k}(f) = (j2\pi fI - A_{k})^{-1} \times \begin{pmatrix} B_{k} \frac{1 - e^{-j2\pi nf_{s}\tau_{k}}}{j2\pi n} e^{-j2\pi nf_{s}\sigma_{k}} + f_{s}G_{k}(f - nf_{s})e^{-j2\pi nf_{s}\sigma_{k}} \\ -f_{s}G_{k+1}(f - nf_{s})e^{-j2\pi nf_{s}\sigma_{k+1}} \end{pmatrix},$$

(2.7)

where  $\tau_k$  is the length of k<sup>th</sup> time interval (see Fig. 2.4) and *I* is an identity matrix.

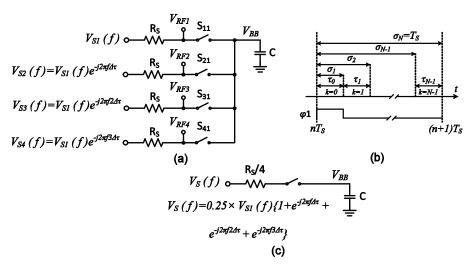

## 2.3.2 Analysis of the Differential Single-Port N-path Filter

We will apply the analysis procedure described in the previous part to derive the output spectrum of the differential N-path filter. Although Fig. 2.3 illustrates a 4-path architecture, analysis is done for a general differential N-path system. At any moment two capacitors are connected to the differential output through two switches, which are activated with the same phase of the input clock.

Figure 2.5. Differential Single-path circuit and the clock phases for the switches.

The resulting time-domain output signal is the superposition of the signals from different capacitors at different moments without any overlap. Since there is no interaction between capacitor voltages, the analysis of the simple network illustrated in Fig. 2.5 suffices, where just one path is illustrated with its timing diagram for the switches. The state equations for this circuit are:

$$\dot{v}_{c}(t) = -\frac{2}{RC}v_{c}(t) + \frac{1}{RC}v_{in}(t) \qquad nT_{s} < t < nT_{s} + \sigma_{1},$$

$$v_{c}(t) = v_{c}(nT_{s} + \sigma_{1}) \qquad nT_{s} + \sigma_{1} < t < nT_{s} + \sigma_{2},$$

$$\dot{v}_{c}(t) = -\frac{2}{RC}v_{c}(t) - \frac{1}{RC}v_{in}(t) \qquad nT_{s} + \sigma_{2} < t < nT_{s} + \sigma_{3},$$

$$v_{c}(t) = v_{c}(nT_{s} + \sigma_{3}) \qquad nT_{s} + \sigma_{3} < t < (n+1)T_{s},$$

(2.8)

where  $v_c(t)$  is the voltage on the capacitor in Fig. 2.5. If one of the two switches is on, the output voltage will track the voltage on the capacitor. When switches are off, the voltage on the capacitor will be held, but will not affect the output. Hence, the output spectrum contribution will be calculated in the track-mode.

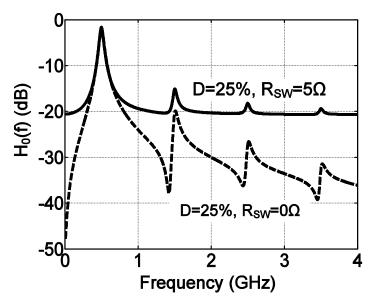

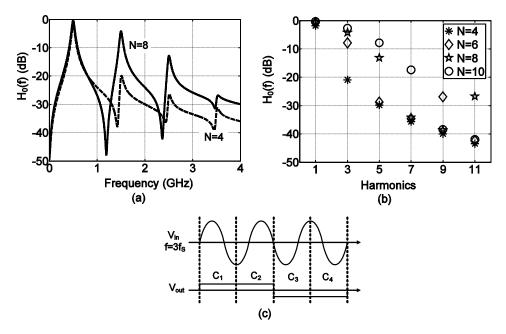

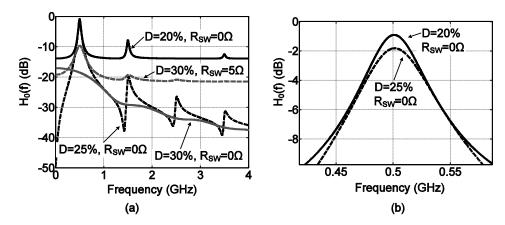

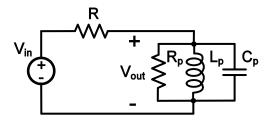

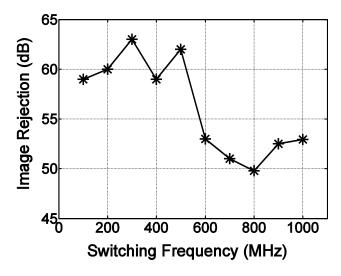

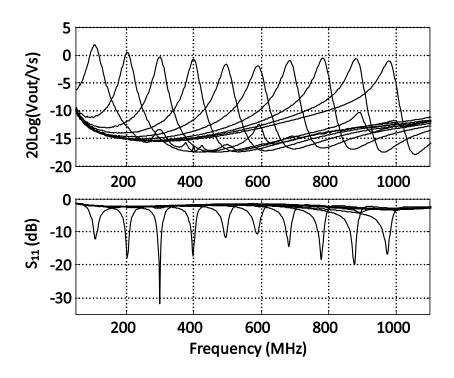

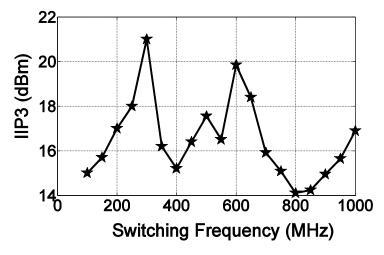

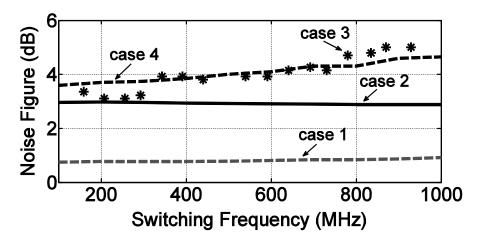

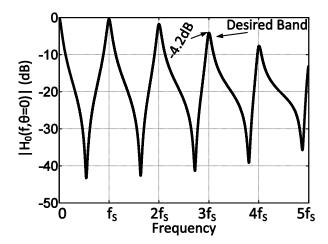

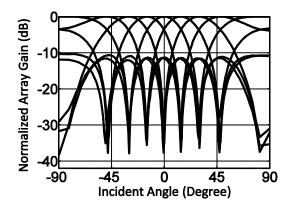

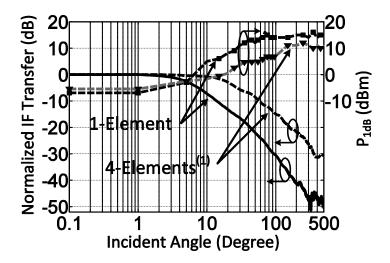

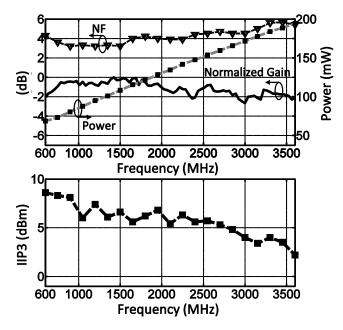

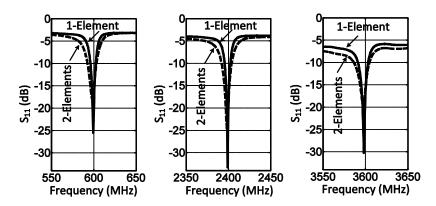

As the capacitor will deliver either  $V_{out}/2$  ( $S_1$  on) or  $-V_{out}/2$  ( $S_2$  on), this contribution is  $v_{out}(t) = 2v_c(t)$ .